board level drop test reliability of ic packages|board level drop testing reliability : importers Abstract: Board level reliability during drop impact is a major concern for electronic . WEBsheilla bellaver sb. @Sheila_bellaver_sbbot. Clique nos 3 pontinhos ↗️ no canto direito e depois em “Abrir pelo navegador”⬇️Link Direto⤵️. http://tinyurl.com/yckfmr2r. Send .

{plog:ftitle_list}

Resultado da Trying is a British comedy television series created by Andy Wolton. The first season premiered on 1 May 2020 on Apple TV+. The second season premiered on 21 May 2021, and the third season premiered on 22 July 2022. In August 2022, Apple announced the show was to be renewed for a fourth .

This paper discusses the effect of board design, the failure mechanism and the board level drop impact performance of two types of common IC packages for hand held electronic product applications namely QFN and CSP, when subjected to the JESD22-B111 .Abstract: Board level reliability during drop impact is a major concern for electronic .

This paper discusses the effect of board design, the failure mechanism and the board level drop impact performance of two types of common IC packages for hand held electronic product.

This paper discusses the effect of board design, the failure mechanism and the board level drop impact performance of two types of common IC packages for hand held . Abstract: Board level reliability during drop impact is a major concern for electronic packages. The impact force generated as the casing strikes the ground can cause . In this work, the dynamic response characteristics of electronic packages when subjected to board level drop impacts are investigated. Initially, board level drop tests are .

Reliability performance of IC packages during drop impact is critical, especially for handheld electronic products. Currently, there is no model that provides good correlation with .

In this paper, reliability performances of board-level chip-scale packages subjected to four JEDEC drop test conditions were evaluated experimentally and numerically. .

This paper aims to discuss the effect of board design, the failure mechanism and the board level drop impact performance of two types of common IC packages for hand held electronic product,. Abstract: This paper discusses the effect of board design, the failure mechanism and the board level drop impact performance of two types of common IC packages for hand .

A simple, easy-to-use and physically meaningful predictive analytical (mathematical) stress model is suggested for the evaluation of the dynamic response of a PCB . In this study, reliability performances of board-level chip-scale packages subjected to four JEDEC drop test conditions: A (500 G; 1.0 ms), B (1500 G; 0.5 ms), F (900 G; 0.7 ms), and H (2900 G; 0.3 ms) were evaluated experimentally and numerically. For each of the test conditions, over 80% of the failed solder joints fractured on the package side. Reliability performance of IC packages during drop impact is critical, especially for handheld electronic products. Currently, there is no model that provides good correlation with experimental measurements of acceleration and impact life. . Board level drop test can be better controlled, compared with system or product level test such as .Unlike component-level reliability testing with BLR, the distinctive requirement is that the component is surface mounted to the test board/interposer, ideally emulating thermo-mechanical stresses that the component would be exposed in the application. (The test board design, construction and materials are selected with this goal.)

micromachine board level drop test

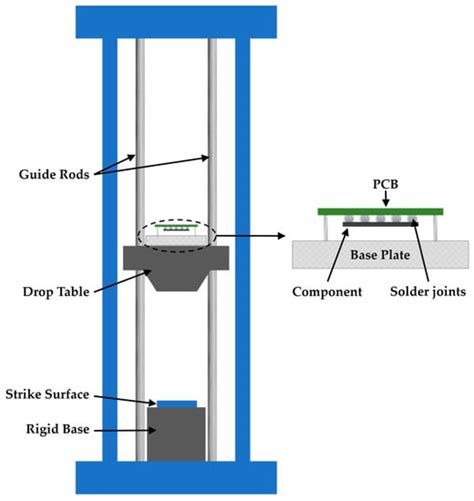

As shown in Fig. 2, the board-level test vehicle is mounted on the base plate with the corners fixed on the standoffs while the base plate is welded to the drop table.Ideally, the standoffs should move synchronously during the drop impact process. Defined by JEDEC [34], [35], an accelerometer is attached to the base plate at a specific location to monitor peak .

board level drop testing reliability

For various electronics packages such as IC and area array packages (BGA, CSP etc.), the reliability of the solder joint during thermal cycling test is a critical issue.of the board-level reliability of such large, ultrathin glass ball grid array (BGA) packages directly mounted onto a system board, considering both their thermal cycling and drop-test performances. To investigate board-level reliability, glass BGA packages, 18.5 × 18.5 mm2 in body size and 100 µm in thickness, Therefore, under the influence of the acceleration of gravity, the weight of the ball grid array(BGA) package, the number of balls, solder ball material, and the solder ball pad size in the drop test are recognized as important factors affecting the .DOI: 10.1016/j.microrel.2007.03.005 Corpus ID: 19096690; Effects of different drop test conditions on board-level reliability of chip-scale packages @article{Lai2008EffectsOD, title={Effects of different drop test conditions on board-level reliability of chip-scale packages}, author={Yi-Shao Lai and Po-Chuan Yang and Chang-Lin Yeh}, journal={Microelectron.

Board level drop test: This test is intended to evaluate and compare drop performance of WLCSPs for handheld electronic product applications in an accelerated test environment, where excessive flexure of a circuit board causes product failure. It is particularly applied to the power Mosfet and analog wafer-level chip-scale package.

Various literatures have been studied to characterize the drop impact model of the printed circuit board used in drop test analysis. Lai et al. [5] investigated board level drop reliability of electronic packaging assemblies subjected to drop testing scenario.The drop testing was carried out with pulse-controlled service condition B specified by the JEDEC standard. Reliability performance of IC packages during drop impact is critical, especially for handheld electronic products. Currently, there is no model that provides good correlation with experimental measurements of acceleration and impact life. . –Cu or Sn–Pb solder joint compositions, fluxes, and substrate pads with Ni/Au surface finish or .

This paper describes the first demonstration of the board-level reliability of such large, ultrathin glass ball grid array (BGA) packages directly mounted onto a system board, considering both their thermal cycling and drop-test performances. To investigate board-level reliability, glass BGA packages, drop test parcel shipments

Drop Test . Board level drop test reliability characterization was performed for all the DOE legs according to the drop test specification [13], with peak acceleration of 1500 G and pulse duration of 1.0 ms as depicted in . Figure 8. Figure 8. Drop shock test condition. The electrical continuity of the WLCSP solder joints was

drop test pdf

Board level reliability during drop impact is a major concern for electronic packages. The impact force generated as the casing strikes the ground can cause electronic device failures in handheld products. The full drop testing procedure is costly and time-consuming due to complex sample preparation and test set-up procedures. Failure analysis also requires . One is the controlled pulse drop at board level modeling and simulation and the other is the free fall board level drop test. The implicit Input-G method is adopted to simulate the board level drop test of an advanced molded leaded package by using the commercial finite element code for the controlled pulse drop test with JEDEC standard. The .

Drop reliability and IC package lifetime should be assessed in the development stage of the mobile product. This requires a database of records of structural designs of the PBA mounting and effective FEA of the drop impact performance for IC packages. . Board Level Drop Test Methods of Components for Handheld Electronic Products, JESD22-B111a .Luan J, Tee TY, Pek E, Lim CT, Zhong ZW. Modal analysis and dynamic responses of board level drop test. In: Proceedings of the 5th electronics packaging technology conference, 2003. p. 233–43. [7] Zhu L, Marcinkiewicz W. Drop impact reliability analysis of CSP packages at board and product system levels through modeling approaches.

The Sn–Bi solder paste is commonly used in electronic assembly and packaging, but its brittleness causes poor reliability in shock environments. In this study, the mechanical reliability of Sn–Bi solder paste and Sn–Bi composite solder paste with thermosetting epoxy (TSEP Sn–Bi) was investigated with the board level drop test. The crack characterizations of . Steps to Successful Board Level Reliability Testing // 5 / 6. Test Setup for BLRT is not Turnkey Finally, once all the test parameters have been selected and success has been confirmed, it is time to perform BLRT. However, testing is not as turnkey as one would expect. 200 mm PCB with assembled drop test IC packages. D.Y.R. Chong et al . In recent years, the board-level drop test has become an essential reliability evaluation methodology in developing mobile devices that involve electronic packages with lead-free solder joints, which, when subjected to dynamic loads, are more fragile than lead-containing ones owing to their high modulus and low ductility.

QFN Package Board Level Reliability Project Call for Participation inar Project Leader: . 2015.7.13 Ver.3. Background •There is an increasing number of IC devices being packaged in no-lead packages such as the Quad Flat No-Lead (QFN) or Micro-Lead Frame (MLF) packages. . much of the existing reliability test data have been generated to .

He started his journey as a camera trainee in a movie. He worked for the International Cinematographer Guild 669 (ICG). There Chad Boyce worked as a second assistant cameraman. He worked there before his death. ICG 669 is . Ver mais

board level drop test reliability of ic packages|board level drop testing reliability